Автоматический синтез сценариев численного моделирования на базе теории вычислительных моделей

Руководитель: Перепёлкин Владислав Александрович

В основе проекта лежит теория вычислительных моделей. Эта теория позволяет вкладывать в компьютер знания в такой форме, что он может автоматически комбинировать эти знания друг с другом и получать (синтезировать) новые решения и новые, более эффективные способы достижения уже существующих. Проект посвящен применению этой теории для автоматизации такого трудоёмкого процесса, как проведение серий численных экспериментов. На этом примере участники проекта познакомятся как с реалиями численного моделирования на параллельных компьютерах, так и тем, как автоматизировать то, что автоматизировать непросто.

Разработка расширения языка фрагментированного программирования LuNA средствами задания рекомендаций по исполнению параллельной программы в терминах событийно-ориентированной модели вычислений

Руководитель: Ткачёва Анастасия Александровна

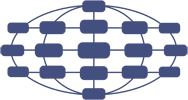

Для повышения эффективности исполнения фрагментированных программ в исходную dataflow модель исполнения вводятся императивные средства. Проект посвящен расширению языка LuNA такими средствами основанными на событийно-ориентированной модели вычислений.

Участники изучат: работу с лексическим и синтаксическим анализаторами flex и bison, принципы создания компилятора и своего языка программирования, особенности dataflow и событийно-ориентированной моделей вычислений

Анализ профиля исполнения параллельных фрагментированных программ

Руководитель: Киреев Сергей Евгеньевич

Цель проекта - создание программы-анализатора, которая должна на основе существующего профиля исполнения параллельной программы (список событий) построить различные характеристики её исполнения (степень загрузки ресурсов, дисбаланс, ...), позволяющие сделать вывод о качестве параллельной реализации.

Проектирование и разработка функциональных блоков клеточно-автоматного процессора на базе технологии ПЛИС

Руководитель: Остапкевич Михаил Борисович

В рамках проекта будет изучено подмножество языка VHDL, изучен набор минимальных функций среды разработчика ISE WebPack, имеющиеся модули разработки, доработаны существующие и разработан новые модули, реализующие разные функции (передача данных, управление, счет, хранение и поиск и т.д.)